Kingswood Consulting - Design Flow

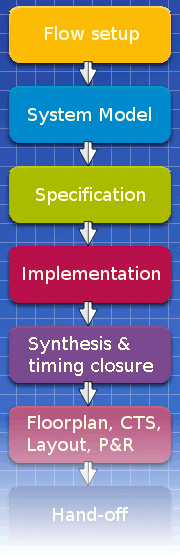

Design Flow

A successful design starts and ends with the right design flow. Most of the design decisions are taken in the early stages of the process, and further development is driven by these early decisions. Making the right choices can make the difference between success and failure of the project.

Flow Setup

Some important early decisions include the choice of:

- Modeling environment: SystemC, C++, Python, MATLAB

- ASIC, FPGA, other electronics or perhaps software?

- Implementation language: VHDL, Verilog, C or others.

- Synthesis and layout tools to use.

System Model

An Electronic System-Level (ESL) model allows early architectural exploration. The ESL model can be used as an executable specification for the implementation that follows.

Using SystemC allows gradual refinement from a data-flow model into a transaction level model, and finally into a cycle accurate model. When suitably wrapped, these models can be co-simulated to verify the implementation, which avoids generating the usually very large test vectors that would otherwise be needed.

At this point the decision is made to partition the design into one or more of:

Specification

A formal specification of the various parts of the design is essential to allow independent development. The specification not only describes what is to be implemented and how, but also the constraints that the system as a whole imposes on each block. A refined system model may be usable as an executable specification and become part of the formal specification.

Implementation

Register Transfer Level (RTL) implementation of a design includes

the development of a testbench for each block. In this testbench,

testvectors or an executable system model are used to exercise the

design, with special consideration of corner cases in the timing

and rounding or wrapping issues in the arithmetic.

Usually, implementation also includes development of block level

timing constraints and block level synthesis.

Synthesis and timing closure

When all the blocks of a design come together, industry standard EDA tools are used to synthesize it. At this point, all the block level timing constraints are merged with I/O and hard macro constraints.

Floorplan, CTS, layout, P&R

Depending on the target technology, the back-end steps of the process may be performed by an external ASIC house or internally.

Copyright 2023, Kingswood Consulting